隨著集成電路工藝制程技術(shù)的不斷發(fā)展,為了提高集成電路的集成度,,同時提升器件的工作速度和降低它的功耗,,半導(dǎo)體工藝的特征尺寸不斷縮小,晶體管的柵,、源和漏有源區(qū)的尺寸也會相應(yīng)縮小,,而它們的等效串聯(lián)電阻會相應(yīng)變大,從而影響電路的速度,。為了改善等效串聯(lián)電阻,,半導(dǎo)體業(yè)界先后發(fā)展出金屬硅化物工藝技術(shù)Polycide和Salicide。

最先出現(xiàn)的金屬硅化物工藝技術(shù)是Polycide工藝技術(shù),,Polycide工藝技術(shù)是為了改善多晶硅柵的等效串聯(lián)電阻和接觸孔的接觸電阻,,Polycide工藝技術(shù)僅僅在多晶硅柵上形成金屬硅化物,源和漏有源區(qū)不會形成金屬硅化物,,所以它沒有辦法改善晶體管源和漏有源區(qū)的等效串聯(lián)電阻和接觸孔的接觸電阻,。為了改善晶體管源和漏有源區(qū)的等效串聯(lián)電阻和接觸孔的接觸電阻而發(fā)展出Salicide工藝技術(shù),Salicide工藝技術(shù)不僅在多晶硅柵上形成金屬硅化物,而且在源和漏有源區(qū)也會形成金屬硅化物,,它同時改善晶體管的柵,、源和漏有源區(qū)的等效串聯(lián)電阻和接觸孔的接觸電阻。

本文摘選自《集成電路制造工藝與工程應(yīng)用》第三章第五節(jié)的內(nèi)容,,這部分內(nèi)容簡單介紹了Polycide工藝技術(shù),、Salicide工藝技術(shù)和SAB工藝技術(shù)的原理,并以納米級工藝形成ESD器件和Non-Salicide器件為例介紹SAB和Salicide工藝技術(shù)的工程應(yīng)用,。

1.1金屬硅化物工藝技術(shù)

首先引起半導(dǎo)體業(yè)界重視的多晶硅柵的等效串聯(lián)電阻,多晶硅柵的電阻率比較高,,雖然柵等效串聯(lián)電阻不會損害電路的直流特性,,但是它會影響器件的高頻特性。在CMOS工藝制程中,,多晶硅柵的厚度是2.5k?~3k?,,對于厚度為3k?的多晶硅柵,它的方塊電阻高達36ohm/sq,。對于一個寬度W=10um和溝道長度L=0.35um的器件,,柵極的串聯(lián)電阻是1028.6ohm/sq,器件柵極等效串聯(lián)電阻會造成非常大的RC延時,。為了降低多晶硅柵和有源區(qū)的方塊電阻,,金屬硅化物(Silicide)工藝技術(shù)被開發(fā)出來并廣范應(yīng)用在半導(dǎo)體工藝制程 。Silicide是由金屬和硅經(jīng)過化學(xué)反應(yīng)形成的一種金屬化合物,,其導(dǎo)電特性介于金屬和硅之間,。最先應(yīng)用于半導(dǎo)體工藝制程的Silicide材料是多晶硅金屬硅化物(Polycide),Polycide是指僅僅在多晶硅柵上形成金屬硅化物,,源和漏有源區(qū)不會形成金屬硅化物,。業(yè)界利用多晶硅和Polycide的雙層結(jié)構(gòu)代替多晶硅柵,從而降低多晶硅的方塊電阻,。Polycide的材料是硅化鎢(WSi2),,對于厚度1K?的多晶硅和1.5K?的Polycide的雙層結(jié)構(gòu)的方塊電阻大約是3ohm/sq。

當半導(dǎo)體工藝的特征尺寸縮小到深亞微米以下時,,晶體管源和漏有源區(qū)的尺寸寬度不斷縮小導(dǎo)致器件的有源區(qū)串聯(lián)電阻不斷增大,,另外后端互連接觸孔的尺寸也不斷縮小,隨著接觸孔尺寸的不斷縮小,,單個接觸孔的接觸電阻也不斷升高,,對于0.25μm工藝技術(shù)平臺的接觸孔,它的尺寸達到0.32μm以下,,單個接觸孔的接觸電阻已經(jīng)升高到200ohm以上了,。為了降低有源區(qū)的串聯(lián)電阻和接觸電阻,,也需要在有源區(qū)上形成金屬硅化物,該技術(shù)是利用金屬(Ti,、Co和NiPt等)與直接接觸的有源區(qū)和多晶硅柵的硅反應(yīng)形成Silicide,,金屬不會與接觸的SiO2、Si3N4和SiON等介質(zhì)材料發(fā)生反應(yīng),,所以Silicide能夠很好地與有源區(qū)和多晶硅柵對準,,把同時在有源區(qū)和多晶硅柵上形成Silicide的技術(shù)稱為自對準金屬硅化物(Self Aligned Silicide - Salicide),。

1.2 Polycide工藝技術(shù)

Polycide工藝技術(shù)是指在器件的柵極上形成金屬硅化物薄膜,,柵極由一定厚度的多晶硅薄膜和金屬硅化物薄膜組成。Polycide工藝技術(shù)僅僅會在多晶硅柵上形成金屬硅化物減小柵極的電阻,,而不會改變有源區(qū)的電阻,。

Polycide工藝技術(shù)主要應(yīng)用在特征尺寸在亞微米的集成電路制造工藝。Polycide工藝技術(shù)的工藝實現(xiàn)過程是首先通過LPCVD淀積多晶硅薄膜,,然后再通過LPCVD在多晶硅上淀積金屬硅化物WSi2薄膜,。WSi2反應(yīng)的氣體源是SiH2Cl2和WF2,反應(yīng)的溫度是550℃,,它的化學(xué)反應(yīng)式是:7SiH2Cl2 2WF6 2WSi2 3SiF4 14HCl,。WSi2的熱穩(wěn)定性非常好,它的阻值并不會隨著工藝溫度而改變,。

硅和金屬硅化物存在相互擴散的問題,,對于Polycide工藝技術(shù),淀積的是WSi2金屬,,多晶硅和WSi2的相互擴散可以促使多晶硅和WSi2更好的結(jié)合,,并不會影響器件性能和柵極的電性。另外,,Polycide只淀積在Poly層上,,多晶硅柵的摻雜類型不會影響Polycide的阻值,所以設(shè)計上不會區(qū)分n型或者p型多晶硅電阻,。

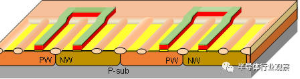

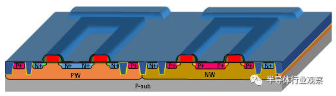

為了更好的理解Polycide工藝技術(shù),,請參考第四章第一節(jié)亞微米工藝中Polycide的工藝步驟。如圖3-103所示,,是亞微米及以上工藝制程技術(shù)形成Polycide的剖面圖,。

圖3-103 亞微米及以上工藝制程技術(shù)形成Polycide的剖面圖

1.3 Salicide工藝技術(shù)

Salicide工藝技術(shù)是在標準的CMOS工藝技術(shù)的基礎(chǔ)上增加硅金屬化的相關(guān)工藝步驟,Salicide工藝步驟是完成源和漏離子注入后進行的,。形成Salicide的基本工藝步驟是首先利用物理氣相淀積(Physical Vapor Deposition - PVD)在多晶硅柵和有源區(qū)上淀積一層金屬(Ti,,Co和NiPt等)。然后進行兩次快速熱退火處理(RTA)以及一次選擇性濕法刻蝕處理,,最終在多晶硅表面和有源區(qū)表面形成Salicide,,金屬硅化物包括TiSi2,CoSi2和NiPtSi等薄膜。金屬Ti,,Co或NiPt不會跟介質(zhì)材料反應(yīng)形成金屬硅化物,,只會與直接接觸的多晶硅和有源區(qū)反應(yīng)形成金屬硅化物。與Polycide不同的是Salicide工藝技術(shù)會在多晶硅和有源區(qū)同時形成Salicide,,降低它們的方塊電阻和接觸電阻,,在設(shè)計上可以得到更小串聯(lián)電阻,減小RC延時,,提高電路的速度,。

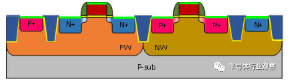

為什么需要兩次RTA呢?以Ti-Salicide工藝為例,,首先淀積一層Ti薄膜,,然后再淀積一層TiN薄膜覆蓋在Ti薄膜上,淀積TiN薄膜的目的是防止Ti在快速熱退火處理時流動,。第一次RTA-1的溫度比較低,,只有450~650℃,Ti只會與有源區(qū)或者多晶硅的硅反應(yīng)形成高阻態(tài)的金屬硅化物Ti2Si,,它是體心斜方晶系結(jié)構(gòu),,它是C49相,Ti不會和氧化硅反應(yīng)生成金屬硅化物,,所以可以利用選擇性濕法刻蝕去除表面的TiN薄膜和氧化硅上沒有反應(yīng)的Ti薄膜,。第二次RTA-2溫度很高,最低也要750℃,,有的工藝平臺要求高達950℃,,RTA-2可以將C49相的高阻態(tài)金屬硅化物Ti2Si轉(zhuǎn)化為低阻的C54相金屬硅化物TiSi2,C54相是面心斜方晶系結(jié)構(gòu),,它的熱力學(xué)特性很好,,非常穩(wěn)定。如果只通過一次RTA生成低阻的金屬硅化物TiSi2,,那么這個步驟的RTA的工藝溫度會很高,,在如此高溫的環(huán)境下,硅可以沿著TiSi2的晶粒邊界進行擴散,,導(dǎo)致氧化硅邊界上面的TiSi2過度生長,,濕法刻蝕無法去除氧化物上的金屬硅化物,而造成短路,。如圖3-104所示,,是經(jīng)過兩次不同溫度的RTA工藝步驟,只在源,、漏和柵上形成Salicide,。如圖3-105所示,,是只經(jīng)過一次高溫的RTA,在STI和側(cè)墻上也形成Salicide,,造成短路,。

圖3-104在源、漏和柵上形成Salicide

圖3-105在STI和側(cè)墻上形成Salicide

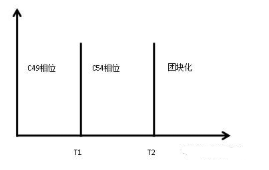

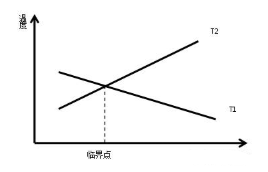

如圖3-106所示,,是Salicide工藝技術(shù)中兩次RTA工藝的溫度相位圖,。第一次RTA-1使金屬與硅反應(yīng)形成相位C49的高阻態(tài)金屬硅化物Ti2Si、Co2Si或者Ni2PtSi,,它的反應(yīng)溫度小于T1,,T1(Ti)> T1(Co)> T1(NiPt)。然后用濕法刻蝕(刻蝕的酸是NH4OH和H2O2)去除氧化物上未反應(yīng)的金屬,,防止橋連短路,。第二次RTA-2需要更高的溫度T2,,把相位C49轉(zhuǎn)化為C54的低阻金屬硅化物生成TiSi2/CoSi2/ NiPtSi2,,T2(Ti)> T2(Co)> T2(NiPt)。

圖3-106 Salicide工藝技術(shù)中兩次RTA工藝的溫度相位圖

Ti-Salicide有一個致命的缺點,,隨著Salicide厚度的降低或者線寬的減小,,Ti-Salicide由C49相位轉(zhuǎn)化為C54相位的臨界溫度T1會升高,而C54相位發(fā)生團塊化的臨界溫度T2反而會降低,,以致于會出現(xiàn)T1=T2的臨界點,,甚至?xí)霈F(xiàn)T2小于T1的情況,如圖3-107所示,,是T1和T2隨silicide厚度或線寬變化圖,。如果出現(xiàn)T2小于T1的情況,Ti-Salicide 出現(xiàn)C49相位后就會直接發(fā)生團塊化,,根本就不存在C54相位這個區(qū)間,,也就是根本找不到降低金屬硅化物電阻的工藝條件,所以只有大尺寸的工藝才會采用Ti-Salicide工藝技術(shù),,例如特征尺寸為0.5μm~0.25μm的工藝技術(shù),。而Co-Salicide可以有效避免這種直接發(fā)生團塊化現(xiàn)象,所以特征尺寸為0.18μm~65nm的工藝技術(shù)都采用Co-Salicide工藝技術(shù),。另外由于特征尺寸為65nm以下的工藝技術(shù)需要特別考慮熱量的問題,,所以選擇NiPt-Salicide工藝技術(shù),因為NiPt-Salicide工藝技術(shù)的RTA工藝溫度比Co-Salicide工藝低,。

圖3-107 T1和T2隨Silicide厚度或線寬變化圖

另外硅和金屬還存在互擴散的問題,,對于Ti-Salicide工藝技術(shù),淀積的金屬是Ti,,在形成硅化物的過程中,,硅是主要擴散物,,在邊緣處可以參與反應(yīng)的硅相對來說會少一點,所以邊緣形成的金屬硅化物的厚度就會相應(yīng)變薄,,那么邊緣的薄層電阻就會相應(yīng)變大,,表現(xiàn)出來的特性就是金屬硅化物的邊緣的電阻較大。對于線寬為0.18μm以下的工藝技術(shù),,這種特性會非常嚴重,。除了邊界處金屬硅化物電阻增大的問題,另外硅會擴散到金屬上,,引起的橋接問題,。由于硅擴散到金屬中的速度大于金屬擴散到硅中的速度,所以金屬硅化物不僅會在金屬與硅的直接接觸面形成,,還會在氧化物上形成造成橋接,,例如STI和側(cè)墻上。雖然STI和側(cè)墻上Ti金屬并不與硅直接接觸,。當初始的硅金屬化反應(yīng)發(fā)生在純N2氣氛中進行時,,可以阻止硅化物在橫向上的生長。另外金屬Co和NiPt可以有效的避免上述效應(yīng),,這是0.18μm ~ 65nm工藝技術(shù)選擇用Co代替Ti的原因,。

Co-Salicide對線寬控制比Ti-Salicide好,RTA1的溫度是300~370℃,,形成C49相位的金屬硅化物Co2Si,,當溫度大約為500℃時Co2Si轉(zhuǎn)化為CoSi,然后在700℃或者更高的溫度下形成C54相位的金屬硅化物CoSi2,。在低溫時Co是主要擴散物,,Co進入界面與硅反應(yīng),這樣Co2Si橫向擴散比Si2Ti的小,,但是在高溫時CoSi轉(zhuǎn)化為CoSi2,,硅是主要擴散物。

摻雜類型會對Salicide的阻值產(chǎn)生影響,,n型區(qū)和p型區(qū)的方塊電阻是不同,。對于n型區(qū),會形成較薄的金屬硅化物,,所以n型區(qū)的方塊電阻較大,,而p型區(qū)的情況相反,所以設(shè)計上要區(qū)分n型或者p型電阻,。

另外雜質(zhì)在Salicide中的擴散速度非??欤栽诙嗑Ч柚械膿诫s物容易進入金屬硅化物層,,而流串至其他地方,。多晶硅會因為摻雜物的流失而產(chǎn)生嚴重的空乏效應(yīng),。對于CMOS工藝,則會有p型和n型摻雜物的相互污染,,導(dǎo)致MOS晶體管的閾值電壓發(fā)生改變,。

對于65nm以下的Ni-Salicide,首先在低溫下形成Ni2Si,,隨著溫度升高再形成NiSi,。由于NiSi具有熱不穩(wěn)定性,當溫度高于400℃時最終形成穩(wěn)定的化合物NiSi2,,在這個過程中Ni是主要擴散物,,導(dǎo)致NiSi2深入襯底形成短路,會形成漏電問題,,這種現(xiàn)象稱為NiSi侵蝕襯底,。為了改善該問題,在Ni靶材中加入5~10%的Pt,,也就是利用NiPt的合金靶材代替純Ni靶材,,最終形成NiPt-Salicide。

1.4 SAB工藝技術(shù)

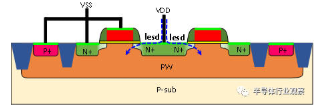

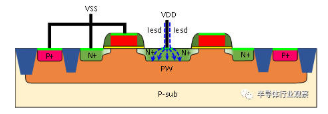

Salicde工藝技術(shù)是利用金屬與多晶硅和有源區(qū)硅反應(yīng),,同時在多晶硅柵和有源區(qū)形成金屬硅化物,,它是自對準的工藝。雖然金屬硅化物可以降低電路的串聯(lián)電阻,,但是金屬硅化物對于ESD器件和較高阻抗的電阻是有害的,為了得到相同的電阻阻值,,金屬硅化物電阻比非金屬硅化物電阻需要更多的面積,,形成金屬硅化物的ESD器件會導(dǎo)致ESD電流在器件表面流動,燒毀ESD器件,。如圖3-108所示,,是ESD電流沿低阻的金屬硅化物表面流動,造成發(fā)熱燒毀器件,。如圖3-109所示,,是在沒有金屬硅化物的區(qū)域,當ESD電流沿有源區(qū)某個方向流動,,造成該方向硅發(fā)熱和電阻升高,,ESD電流會更傾向于流向電阻低的區(qū)域,所以ESD電流會沿有源區(qū)各個方向均勻地流動,,從而達到保護器件的目的,。

圖3-108 ESD電流沿金屬硅化物表面流動

圖3-109 ESD電流沿有源區(qū)各個方向流動

為了得到高阻抗的有源區(qū)電阻、高阻抗的多晶硅電阻和高性能的ESD器件,,需要形成較高阻抗的非金屬硅化物區(qū)域,,通常把這些較高阻抗的區(qū)域稱為Non-Salicide區(qū)域,,把這些沒有形成金屬硅化物的器件稱為Non-Salicide器件。為了形成Non-Salicide器件,,需要利用金屬只會與多晶硅和有源區(qū)硅反應(yīng)而不會與介質(zhì)層反應(yīng)的特點,,在進行Salicide工藝流程前淀積一層介質(zhì)層覆蓋在Non-Salicide區(qū)域,防止這些區(qū)域形成Salicide,,這種為了形成Non-Salicide器件的技術(shù)稱為自對準硅化物阻擋層技術(shù)(Self-Aligned Block - SAB),,也可以稱為電阻保護氧化層(Resist Protection Oxide - RPO)。SAB薄膜的材料包括富硅氧化物SRO(Silicon Rich Oxide),、SiO2,、SiON和Si3N4。其中,,SRO薄膜的硅含量比常規(guī)的氧化硅薄膜大,,SRO的制備與常規(guī)氧化硅大致相同,都可以通過PECVD淀積,,氣體源是SiH4,、O2和Ar。其中SiH4和O2的比率設(shè)置成高于形成常規(guī)氧化硅所用的比率,,另外可以用Si2H6和TEOS(四乙基硅烷)取代SiH4,,也可以用N2O或者O3取代O2。淀積SiON的氣體源是SiH4,、N2O和Ar,,淀積Si3N4的氣體源是SiH4、N3H和Ar,。

為了得到Non-Salicide器件,,需要在傳統(tǒng)的CMOS工藝流程中增加一道SAB工藝步驟。SAB的工藝流程包括利用PECVD淀積硅化物例如SRO或者SiO2,,還有SAB光刻處理(保留Non-Salicide區(qū)域光刻膠,,去掉Salicide區(qū)域光刻膠),以及SAB刻蝕處理(去掉Salicide區(qū)域的氧化硅,,為下一步形成Salicide做準備),。SAB刻蝕處理包括干法刻蝕和濕法刻蝕。

為什么SAB刻蝕利用干法刻蝕和濕法刻蝕結(jié)合呢,?因為干法刻蝕是利用帶電離子漿轟擊的方式去除氧化硅,,它既包括物理的轟擊也包括化學(xué)反應(yīng)的過程,如果直接用干法刻蝕完全去除氧化硅會損傷襯底硅,,導(dǎo)致最終形成的Salicide電阻偏高,。而濕法刻蝕是利用化學(xué)反應(yīng)去除氧化硅,不存在物理轟擊,,所以不會損傷襯底,。但是干法刻蝕是各向異性刻蝕,,它的刻蝕方向是垂直向下,它能很好地控制尺寸,,而濕法刻蝕是各向同性刻蝕,,濕法刻蝕橫向刻蝕比較嚴重,不能控制刻蝕的方向,,最終刻蝕得到的尺寸會與設(shè)計的圖形存在偏差,,另外橫向刻蝕還會滲透到柵氧里面導(dǎo)致漏電,器件失效,。所以SAB刻蝕步驟需要干法刻蝕和濕法刻蝕結(jié)合,。

1.5 SAB和Salicide工藝技術(shù)的工程應(yīng)用

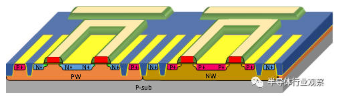

SAB和Salicide工藝技術(shù)一般用在深亞微米及其以下的工藝中,為了更好的理解SAB和Salicide工藝技術(shù),,下面以納米級工藝形成ESD器件和Non-Salicide器件為例介紹它們的工程應(yīng)用,。

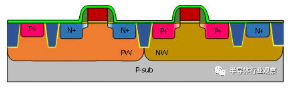

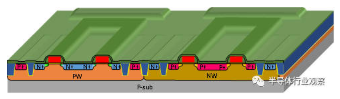

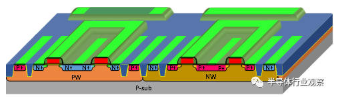

a)選取已經(jīng)形成重摻雜源漏有源區(qū)的工藝流程為起點。如圖3-110所示,,是形成重摻雜源漏有源區(qū)的剖面圖,。

圖3-110 形成重摻雜源漏有源區(qū)的剖面圖

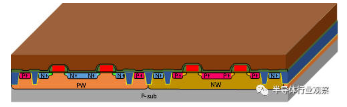

b)淀積SAB。利用PECVD淀積一層SiO2,,目的是形成SiO2覆蓋在不需要形成金屬硅化物(Salicide)的有源區(qū)和多晶硅表面,,防止它們形成Salicide。如圖3-111所示,,是淀積SiO2的剖面圖,。

圖3-111淀積SiO2的剖面圖

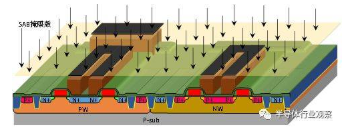

c)SAB光刻處理。通過微影技術(shù)將SAB掩膜版上的圖形轉(zhuǎn)移到晶圓上,,形成SAB的光刻膠圖案,,非SAB區(qū)域上保留光刻膠。如圖3-112所示,,是涂光刻膠的剖面圖。如圖3-113所示,,是SAB光刻的剖面圖,。

圖3-112涂光刻膠的剖面圖

圖3-113 SAB光刻的剖面圖

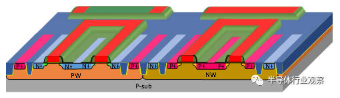

d)SAB刻蝕處理。干法刻蝕和濕法刻蝕結(jié)合,,把沒有被光刻膠覆蓋的SiO2清除,,裸露出需要形成Salicide的有源區(qū)和多晶硅,為下一步形成Salicide做準備,。如圖3-114所示,,是SAB刻蝕的剖面圖。

圖3-114 SAB刻蝕的剖面圖

e)去除光刻膠,。利用干法刻蝕和濕法刻蝕去除光刻膠,。如圖3-115所示,,是去除光刻膠的剖面圖。

圖3-115去除光刻膠的剖面圖

f)清洗自然氧化層,。利用化學(xué)溶液NH4OH和HF清除自然氧化層,,因為后面一道工藝是淀積NiPt,把硅表面的氧化物清除的更干凈,,使NiPt跟襯底硅和多晶硅的清潔表面接觸,,更易的形成金屬硅化物,所以淀積NiPt前再過一道酸槽清除自然氧化層,。

g)淀積NiPt和TiN,。利用PVD濺射工藝淀積一層厚度約100?的NiPt和厚度約250?的TiN,TiN的作用是防止NiPt在RTA階段流動導(dǎo)致金屬硅化物厚度不一,,電阻值局部不均勻,。如圖3-116所示,是淀積NiPt和TiN的剖面圖,。

圖3-116淀積NiPt和TiN的剖面圖

h)第一步Salicide RTA1,。在高溫約200~300℃的環(huán)境下,通入N2使NiPt與有源區(qū)和多晶硅反應(yīng)生成高阻的金屬硅化物Ni2PtSi,。

i)NiPt和TiN 選擇性刻蝕,。利用濕法刻蝕清除TiN和沒有與硅反應(yīng)的NiPt,防止它們橋連造成電路短路,。如圖3-117所示,,是選擇性刻蝕的剖面圖。

圖3-117選擇性刻蝕的剖面圖

j)第二步Salicide RTA2,。在高溫約400~450℃的環(huán)境下,,通入N2把高阻態(tài)的Ni2PtSi轉(zhuǎn)化為低阻態(tài)的NiPtSi2。